ASML plánuje široké využití technologie High‑NA EUV již příští rok pro výrobu čipů s velikostí tranzistoru 1,4 nm a menší.

Krátké shrnutí

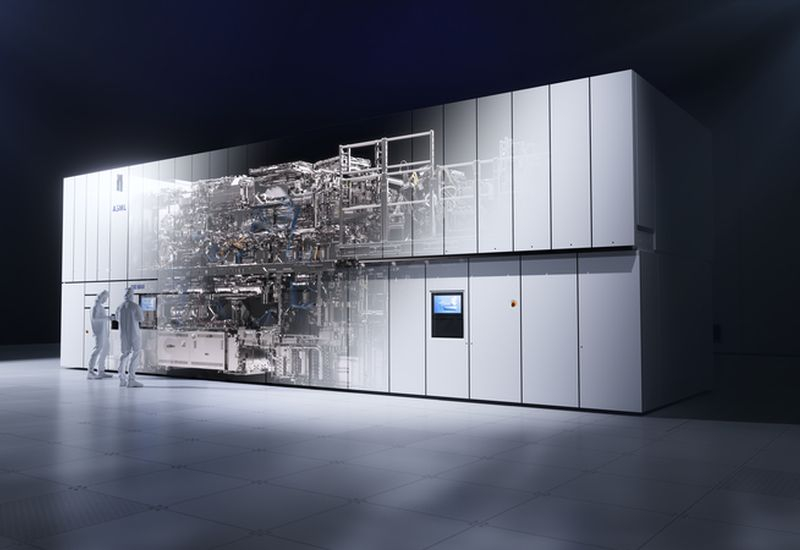

Nová fáze miniaturizace mikročipů vyžaduje přechod k pokročilejším metodám litografie. V následujících dvou letech by měla průmyslová odvětví spustit výrobu čipů s využitím zařízení třídy High‑NA EUV, které umožňuje dosáhnout velikostí do 8 nm při jednom průchodu a otevírá cestu k procesům 1,4 nm a méně než 10 nm (DRAM).

1. Technologické možnosti High‑NA EUV

Parametr | Hodnota

Číslová apertura (NA) | 0,55

Minimální velikost za jeden průchod | ≤ 8 nm

Možné technologické procesy | 1,4 nm (integrované obvody), < 10 nm (DRAM)

Tyto charakteristiky činí zařízení ASML Twinscan EXE:5200B a podobná řešení kriticky důležitými pro budoucí mikroelektronické technologie.

2. Klíčoví hráči

Společnost | Stav zavedení | Komentář

ASML | Výrobce High‑NA EUV | První klienti: Intel, Samsung, SK Hynix

TSMC | Ne připraven na masové využití | Cena jednoho systému – 380 mil USD; plánuje se odklonit od 1,4 nm čipů

Intel | V prosinci 2023 uvedl Twinscan EXE:5200B | Připrava na vydání technologie 14A a související zařízení

Samsung Electronics | Obdržel první skener v prosinci 2023; druhý – v tomto pololetí | Plánuje jej použít pro Exynos 2600 (2 nm) a budoucí procesory Tesla

SK Hynix | Ovládá High‑NA EUV od září 2023 | Již používá běžnou EUV litografii v DRAM (10 nm), plánuje použít minimálně pět vrstev EUV pro 6. generaci

Micron Technology | Dosud nerozhodl o termínech zavedení | Možné plány na High‑NA EUV

Rapidus (Japonsko) | Ovládá technologii 2 nm; plánuje 1,4 nm v roce 2029 | Do roku 2027 by měl spustit masovou výrobu 2 nm čipů na Hokkaidě

3. Ekonomické aspekty

* Cena zařízení – jeden systém High‑NA EUV stojí přibližně 380 mil USD.

* Přechod k dražšímu vybavení zvyšuje výrobní náklady, což se nakonec odráží na spotřebitelích.

* Proto velcí výrobci (TSMC, Rapidus) projevují opatrnost a plánují zavedení postupně.

4. Očekávané termíny

Nové litografické skenery ASML pro masovou výrobu špičkových polovodičových produktů začnou být aktivně používány v letech 2027–2028. Do té doby budou společnosti postupně přizpůsobovat své výrobní linky, integrovaním High‑NA EUV do stávajících technologických procesů.

Závěr

Přechod na High‑NA EUV je klíčovým krokem k dosažení velikostí do 1,4 nm a kompaktnějších DRAM. Největší světoví hráči již zahájili přípravné práce, ale masové zavedení se očekává až za několik let kvůli vysokým nákladům a nutnosti adaptace výrobních řetězců.

Asted Cloud

Asted Cloud

Komentáře (0)

Podělte se o svůj názor — prosím, buďte slušní a držte se tématu.

Přihlaste se pro komentování